从20 世纪80 年代中期模拟蜂窝式移动电话通信系统开始,移动通信系统已经演进到了第五代。通过引入数字调制,信道编码,多输入多输出正交频分复用等新的技术,移动通信系统正变得日益强大以满足人们不断增长的通信需求。相对于第四代移动通信系统,第五代移动通信系统(5G)需要提供更高的传输速率,更小的延时以及更强大的设备连接能力,这对通信系统的设计带来了新的挑战[1-3]。

LDPC码在20世纪60年代被Gallager提出[4-5],但是由于其较高的编码复杂度,一直到1996年才被MacKay重新发现。准循环低密度奇偶校验(quasi-cyclic low-density parity-check,QC-LDPC) 码是一类校验矩阵具有特殊规则性的LDPC码,能够极大地降低编译码器的复杂度,广泛的被IEEE 802.16e (WiMAX), IEEE 802.11n (WLAN) 和5G标准采用[6]。随着大规模集成电路的快速发展,高效的LDPC码编译码器的实现一直是LDPC码应用研究的一个焦点[7-10]。在编码器的实现上,不适宜采用直接将信息序列与生成矩阵相乘方法,因为这种方法所需的数据存储量和逻辑单元消耗量随着码长的增加平方递增,在码长较长的情况下会导致复杂度过高而无法实现。为了实现低复杂度的快速编码,研究工作逐渐转向结构化的编码方法。针对具有准循环结构的LDPC码,文献[11]提出了一种快速递归编码算法和它的硬件实现架构,而在相同的算法下,文献[12]又提出了一种串行结构的编码器,其结构易于理解和实现,但同时带来了较长的路径延时。文献[13]在快速递归编码算法的基础上提出了一种快速流水线双向递归编码算法和相应的编码器结构,这种编码器通过递归计算校验向量的每一个分量并采用流水线技术增加了编码器的吞吐率,而较长的关键路径限制了其吞吐量的提升。随着5G标准的制定,大量的研究工作开始转向5G标准下LDPC码编译码的研究与实现[14-17],文献[16-17]对适用于5G标准的编码器进行了研究,能够完成对5G标准下LDPC码的编码,但是它们较长的处理时延无法满足5G通信系统的需求。

本文针对5G标准下LDPC码的编码技术进行了分析和研究,改进了现有的5G标准下LDPC码编码算法的算法流程,提出了一种高并行度的LDPC码编码算法并进行了硬件实现。改进的算法具有更高的并行度从根本上降低编码的时延,硬件架构的高的灵活性可以满足5G通信系统的各项要求,同时多路并行的运算结构可以大幅度的降低编码时延提高编码器的吞吐率。

QC-LDPC码是一类适合于硬件实现的LDPC码,它的特点是校验矩阵H由许多的子矩阵所构成,每个子矩阵为零矩阵,单位阵和单位阵的右循环移位矩阵中的一种。校验矩阵可由基矩阵Hb扩展得到,Hb中的每个元素都与校验矩阵H中相同位置关系的![]() 子矩阵一一对应,元素的值只有0 或1 两种,分别表示相应位置的

子矩阵一一对应,元素的值只有0 或1 两种,分别表示相应位置的![]() 子矩阵为零矩阵或非零矩阵。由于基矩阵无法具体描述校验矩阵子矩阵的右循环移位特性,需要引入循环移位矩阵Hp。Hp和Hb大小相同,不同的是Hp中分别用-1和具体的右循环移位数值x表示该元素在H中相应的

子矩阵为零矩阵或非零矩阵。由于基矩阵无法具体描述校验矩阵子矩阵的右循环移位特性,需要引入循环移位矩阵Hp。Hp和Hb大小相同,不同的是Hp中分别用-1和具体的右循环移位数值x表示该元素在H中相应的![]() 子矩阵为零矩阵或向右循环移位x位的单位矩阵。对于QC-LDPC码,每个校验矩阵H都对应唯一的循环移位矩阵Hp,它的特性也可以通过Hp研究和表示,为简明起见下面均通过循环移位矩阵来表述校验矩阵的相关特性。

子矩阵为零矩阵或向右循环移位x位的单位矩阵。对于QC-LDPC码,每个校验矩阵H都对应唯一的循环移位矩阵Hp,它的特性也可以通过Hp研究和表示,为简明起见下面均通过循环移位矩阵来表述校验矩阵的相关特性。

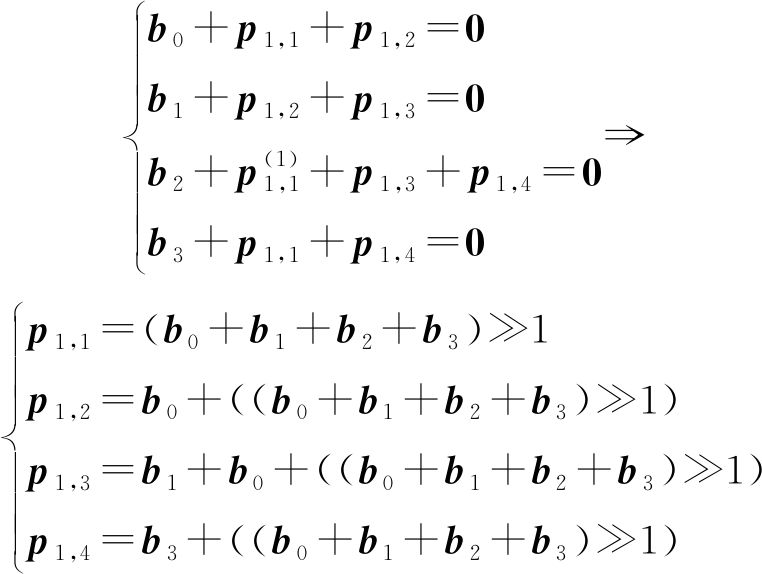

循环移位矩阵Hp可被分解为系统位部分Hp1和校验位部分Hp2,如式(1)所示,其中![]() 为信息位长度k在基矩阵中的映射长度,

为信息位长度k在基矩阵中的映射长度,![]() 为校验位长度p在基矩阵中的映射长度。

为校验位长度p在基矩阵中的映射长度。

Hp=[(Hp1)mb×kb|(Hp2)mb×mb]

(1)

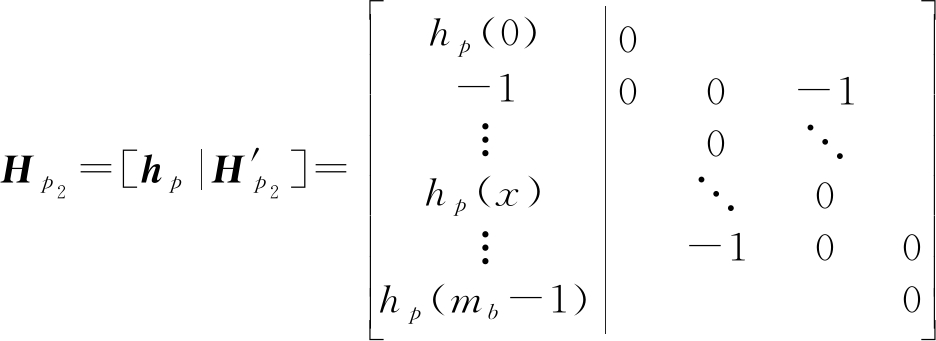

将Hp2继续分解为向量hp与子矩阵![]() 若Hp2的结构满足如下双对角特性:1) hp中只有三个不为-1的分量,其中两个分量为hp(0)和hp(mb-1),且最后一个不为-1的分量被记为hp(x)。2)H′p2为双对角矩阵,即用i, j分别表示

若Hp2的结构满足如下双对角特性:1) hp中只有三个不为-1的分量,其中两个分量为hp(0)和hp(mb-1),且最后一个不为-1的分量被记为hp(x)。2)H′p2为双对角矩阵,即用i, j分别表示![]() 的行与列,满足当i=j或i=j+1时H′p2(i, j)=0,其余位置为-1,如式(2)所示。具有上述特性循环移位矩阵的QC-LDPC码称为准循环双对角LDPC码。

的行与列,满足当i=j或i=j+1时H′p2(i, j)=0,其余位置为-1,如式(2)所示。具有上述特性循环移位矩阵的QC-LDPC码称为准循环双对角LDPC码。

(2)

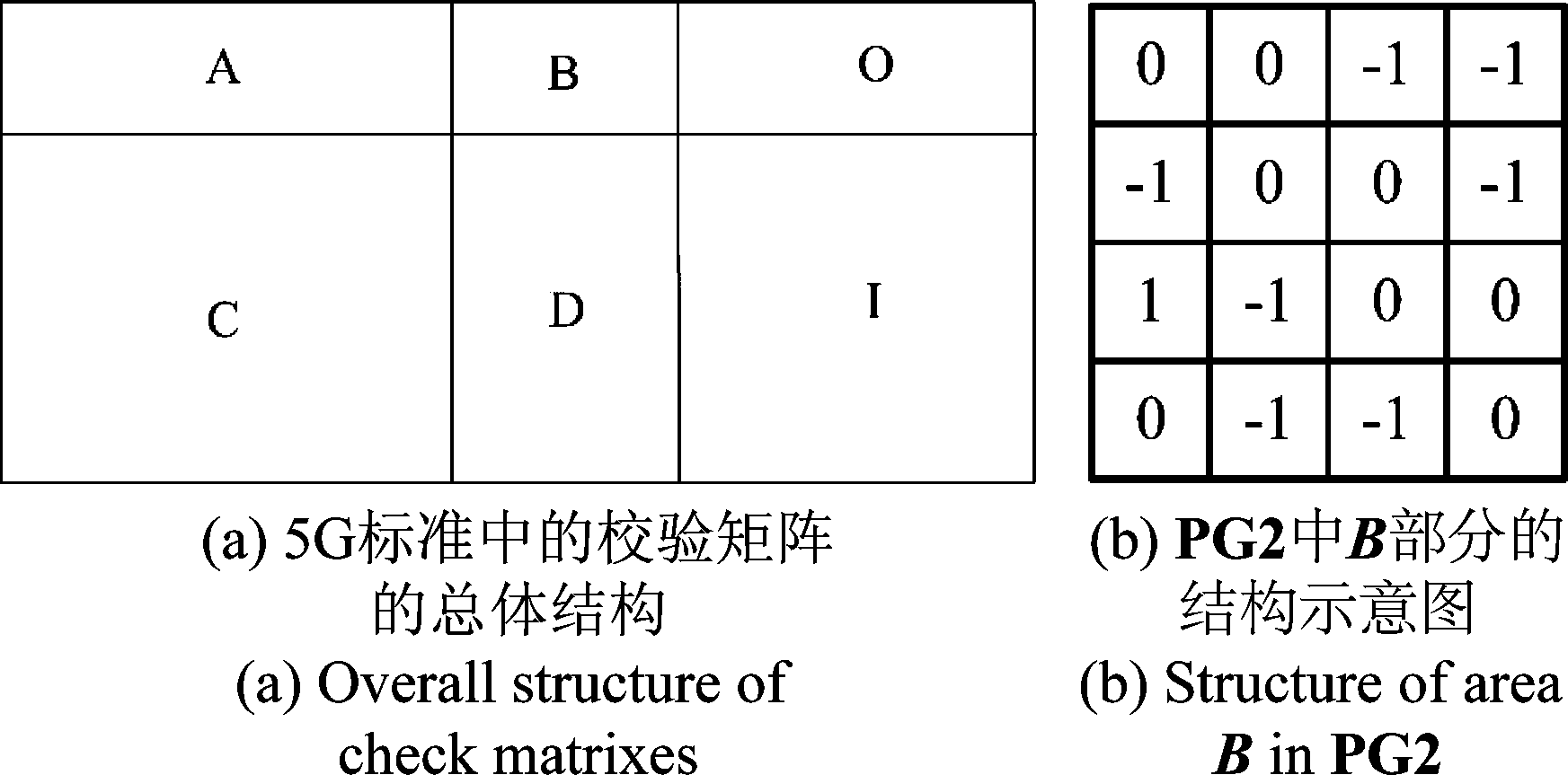

5G标准下的LDPC码本质上是一种QC-LDPC码,由大小为46×68的基矩阵BG1或42×52的基矩阵BG2扩展得到,与基矩阵对应的循环移位矩阵记为PG1和PG2。以PG2为例,5G标准中校验矩阵的结构可以分为六个区域表示为图1(a)的形式, A和C区域由0,-1和正整数组成对应校验矩阵中相应区域![]() 的单位阵,单位阵的右循环移位矩阵和零矩阵组成的矩阵阵列,O区域为零矩阵, I区域为单位矩阵也称为单对角结构。B区域是一个大小为4×4矩阵且满足双对角特性,具体如式(3)所示,b1是一个有三个元素不为-1的4 维的向量且满足b(1)≠-1和b(3)≠-1,剩余的一个不为-1的位置被记为x,B2是一个4×3的双对角矩阵,用i与j分别表示矩阵的行与列,满足当i=j或i=j+1时B2(i, j)=0,其余位置为-1, 如图1(b)所示。为了支持灵活的编码码率,5G校验矩阵在设计时采用了扩展的方式,矩阵的[A B]区域称为核矩阵,对应一个高码率的准循环双对角LDPC码,[C D I]为扩展矩阵,对应扩展的冗余校验比特,编码时通过选择扩展矩阵行列数就可以得到所需的相应低码率LDPC码校验矩阵。

的单位阵,单位阵的右循环移位矩阵和零矩阵组成的矩阵阵列,O区域为零矩阵, I区域为单位矩阵也称为单对角结构。B区域是一个大小为4×4矩阵且满足双对角特性,具体如式(3)所示,b1是一个有三个元素不为-1的4 维的向量且满足b(1)≠-1和b(3)≠-1,剩余的一个不为-1的位置被记为x,B2是一个4×3的双对角矩阵,用i与j分别表示矩阵的行与列,满足当i=j或i=j+1时B2(i, j)=0,其余位置为-1, 如图1(b)所示。为了支持灵活的编码码率,5G校验矩阵在设计时采用了扩展的方式,矩阵的[A B]区域称为核矩阵,对应一个高码率的准循环双对角LDPC码,[C D I]为扩展矩阵,对应扩展的冗余校验比特,编码时通过选择扩展矩阵行列数就可以得到所需的相应低码率LDPC码校验矩阵。

B=[(b1)4×1|(B2)4×3]

(3)

图1 5G标准中的校验矩阵结构示意图

Fig.1 Structure of the check matrixes in 5G standard

文献[16],[17]中已经提出了可以适用于5G通信系统编码算法,但是其中所采用的编码流程并没有完全发挥算法的并行度。通过对算法流程进行的改进,本文提出的高并行度的LDPC码编码算法可以进一步减小算法的时延。由于PG1和PG2结构上相同且PG2中信息位对应的列数kb会随着不同的信息位长度变化,情况更为复杂,所以下面将以PG2为例对编码算法过程进行详细阐述。

根据校验矩阵的不同结构码字可以被分为信息位部分s,校验位第一部分p1和校验位第二部分p2,分别与校验矩阵的 和

和![]() 区域相对应,s,p1和p2按照扩展因子

区域相对应,s,p1和p2按照扩展因子![]() 的大小分别分为kb,4和mb-4块

的大小分别分为kb,4和mb-4块![]() 维子向量。

维子向量。

cT=[s| p1|p2]T=

[s0,s1,…,skb-1|p1,0,p1,1,p1,3,p1,4|p2,0,p2,1,…,p2,mb-5]T

(4)

又因为

(5)

经过推导可以容易的得到

(6)

自然的可以将编码过程分为两个主要部分分别求解校验位第一部分p1和校验位第二部分p2。

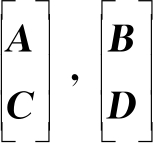

利用矩阵求逆直接求解p1会导致巨大的的硬件资源消耗,此时可以利用B区域的特殊结构来避免。PG2中B区域的取值情况有两种,以图1(b)的情况为例。首先设Ai, j为PG2的A区域中第i行第j列元素在校验矩阵中对应的![]() 子矩阵,Bi, j为B区域元素所对应的

子矩阵,Bi, j为B区域元素所对应的![]() 子矩阵,并设

子矩阵,并设![]() 由于Ai, j为零矩阵或向右循环移位x位的单位矩阵,可以得到Ai, jsj和Bi, jp1, j结果为零向量或sj,p1, j进行循环移位后的向量。进而通过等式

由于Ai, j为零矩阵或向右循环移位x位的单位矩阵,可以得到Ai, jsj和Bi, jp1, j结果为零向量或sj,p1, j进行循环移位后的向量。进而通过等式![]() 可以容易的得到bi与p1,1,p1,2,p1,3和p1,4的对应关系如式(7)左边方程组表示,

可以容易的得到bi与p1,1,p1,2,p1,3和p1,4的对应关系如式(7)左边方程组表示,![]() 为p1的第一个分量p1,1向左循环移动1 次后的向量。此时如果按照文献[13]提出的快速流水线双向递归编码对p1,k(1≤k≤4)中各个分量的递归求解会带来巨大的延迟,为了解决这个问题将式(7)左边方程组进行简单变换后可得到右边的等价形式。通过等价形式可以很明显的看出p1,1,p1,2,p1,3和p1,4为bi(0≤i≤3)模二加并移位后的结果,又因为bi(0≤i≤3)为信息序列和校验矩阵子矩阵的矩阵乘积之和可以同时求解得到,所以可以同时求解 p1,1,p1,2,p1,3和p1,4得到p1,这种同时求解四个分量的方式被称为四路并行的方式,p2可以在p1的计算以后根据式(6)中的关系

为p1的第一个分量p1,1向左循环移动1 次后的向量。此时如果按照文献[13]提出的快速流水线双向递归编码对p1,k(1≤k≤4)中各个分量的递归求解会带来巨大的延迟,为了解决这个问题将式(7)左边方程组进行简单变换后可得到右边的等价形式。通过等价形式可以很明显的看出p1,1,p1,2,p1,3和p1,4为bi(0≤i≤3)模二加并移位后的结果,又因为bi(0≤i≤3)为信息序列和校验矩阵子矩阵的矩阵乘积之和可以同时求解得到,所以可以同时求解 p1,1,p1,2,p1,3和p1,4得到p1,这种同时求解四个分量的方式被称为四路并行的方式,p2可以在p1的计算以后根据式(6)中的关系![]() 求得。

求得。

(7)

通过上述对算法过程,可以总结出对5G标准中的LDPC码进行编码最主要的是求解p1,CsT和![]() 三部分。在文献中[17]中对这三部分是按p1,CsT和

三部分。在文献中[17]中对这三部分是按p1,CsT和![]() 的顺序依次求解,而在文献[16]中则将p1,CsT同时求解,待两部分都求解完成后再求解

的顺序依次求解,而在文献[16]中则将p1,CsT同时求解,待两部分都求解完成后再求解![]() 但是采用上述算法流程在实现时并不能完全发挥编码算法的并行度,通过对算法流程优化可以进一步减小算法的延时。首先将矩阵的C和D部分按照行号由低到高每四行构成4×kb的子矩阵Ci和4×4的子矩阵Dj,当本次编码选取的C,D部分的行数可能不能被4整除时,将余下的行数构成的矩阵记为Cf和Df。这样将完整的编码过程分为三步,第一步同时求解p1和C1sT;第二步求解

但是采用上述算法流程在实现时并不能完全发挥编码算法的并行度,通过对算法流程优化可以进一步减小算法的延时。首先将矩阵的C和D部分按照行号由低到高每四行构成4×kb的子矩阵Ci和4×4的子矩阵Dj,当本次编码选取的C,D部分的行数可能不能被4整除时,将余下的行数构成的矩阵记为Cf和Df。这样将完整的编码过程分为三步,第一步同时求解p1和C1sT;第二步求解![]() 并将其与先前得到的C1sT进行模二加法运算得到p2部分的第一组4个分量p2,1~p2,4;第三步并行求解

并将其与先前得到的C1sT进行模二加法运算得到p2部分的第一组4个分量p2,1~p2,4;第三步并行求解![]() 和CisT(i>1, j>1)并将它们相异或得到p2部分的一组分量直至求解

和CisT(i>1, j>1)并将它们相异或得到p2部分的一组分量直至求解![]() 拼接得到完整的p2,最后将s,p1,p2 拼接起来得到码字c。采用这种算法流程可以将p1,CsT和

拼接得到完整的p2,最后将s,p1,p2 拼接起来得到码字c。采用这种算法流程可以将p1,CsT和![]() 三部分的求解过程的并行度进一步提高,并且按照这种流程进行合理设计的硬件结构能够同时在吞吐率,灵活性和硬件资源利用率三方面找到平衡点。

三部分的求解过程的并行度进一步提高,并且按照这种流程进行合理设计的硬件结构能够同时在吞吐率,灵活性和硬件资源利用率三方面找到平衡点。

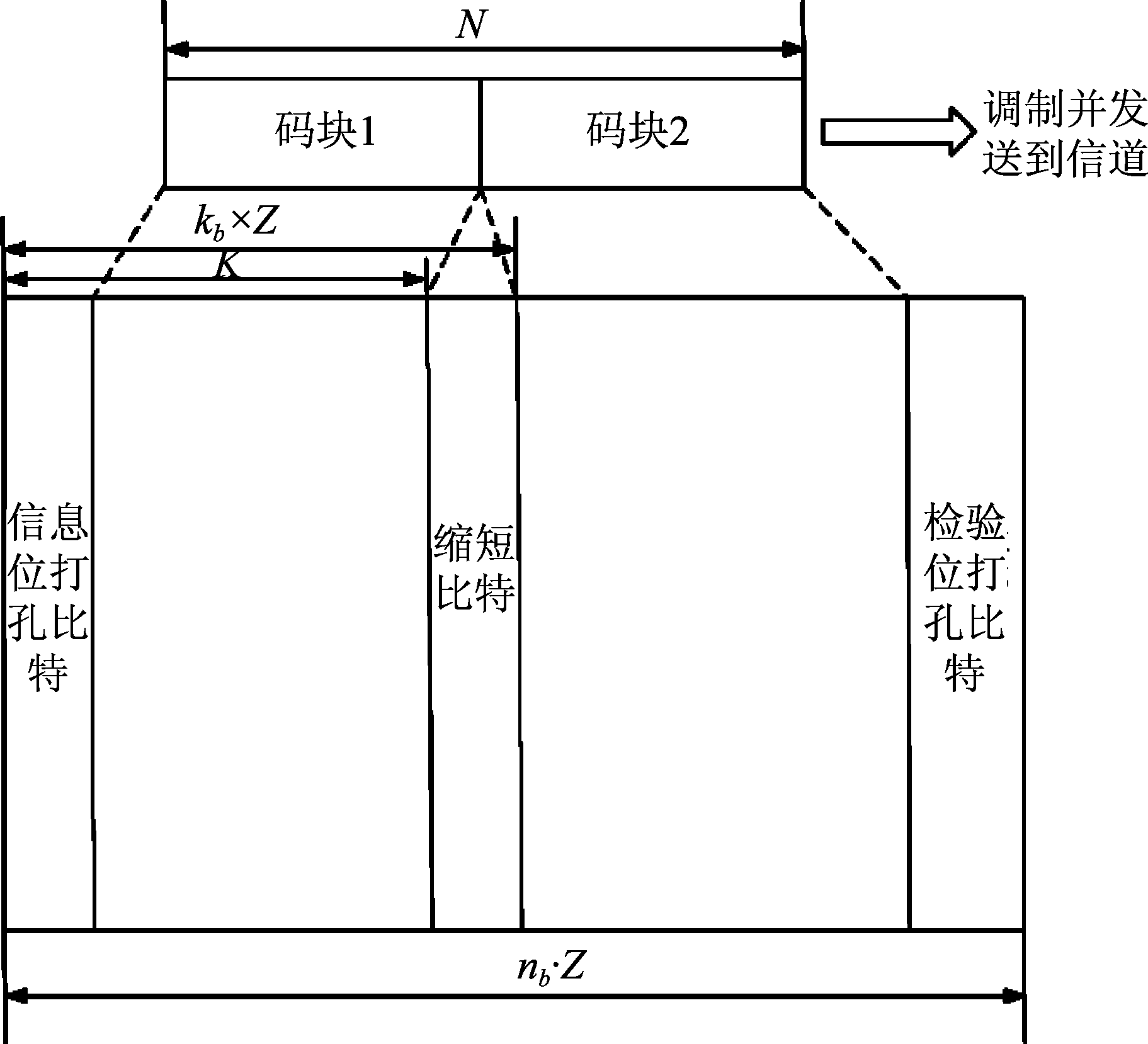

为了与复杂的信道状况相匹配,完整编码过程还包括了对信息位的打孔和缩短以及校验位的打孔。信息位缩短在开始编码之前,通过在信息位比特末尾补0使其达到矩阵所需的比特长度,信息位和校验位的打孔是在完成编码后将放弃将完整码字c相应位置的部分比特送入信道中使编码比特数和信道资源相匹配,过程示意图如图2所示。信息位打孔比特数Npunc1,信息位缩短比特数Npadd,校验位打孔比特数Npunc2分别由式(8)~(10)计算得到,其中![]() 为扩展因子,kb,nb分别为信息位长度k和码长N在循环移位矩阵中的映射长度,完成速率匹配后实际进入信道中的码字个数为N。

为扩展因子,kb,nb分别为信息位长度k和码长N在循环移位矩阵中的映射长度,完成速率匹配后实际进入信道中的码字个数为N。

(8)

(9)

(10)

图2 5G LDPC 码的打孔与缩短示意图

Fig.2 Padding and Puncturing in 5G LDPC encoding

总体来说,本文提出的高并行度的LDPC码编码算法在过程上满足5G标准中LDPC码对编码的各项要求,![]() 位一组的求解方式便于在硬件结构实现上兼容不同的码长和码率,分段求解校验位可以满足IR-HARQ方案将信息比特与校验比特分为多个冗余版本分段传送的需要,最重要的是通过将部分求解过程并行化进一步提高了算法的并行度,降低了算法时延。

位一组的求解方式便于在硬件结构实现上兼容不同的码长和码率,分段求解校验位可以满足IR-HARQ方案将信息比特与校验比特分为多个冗余版本分段传送的需要,最重要的是通过将部分求解过程并行化进一步提高了算法的并行度,降低了算法时延。

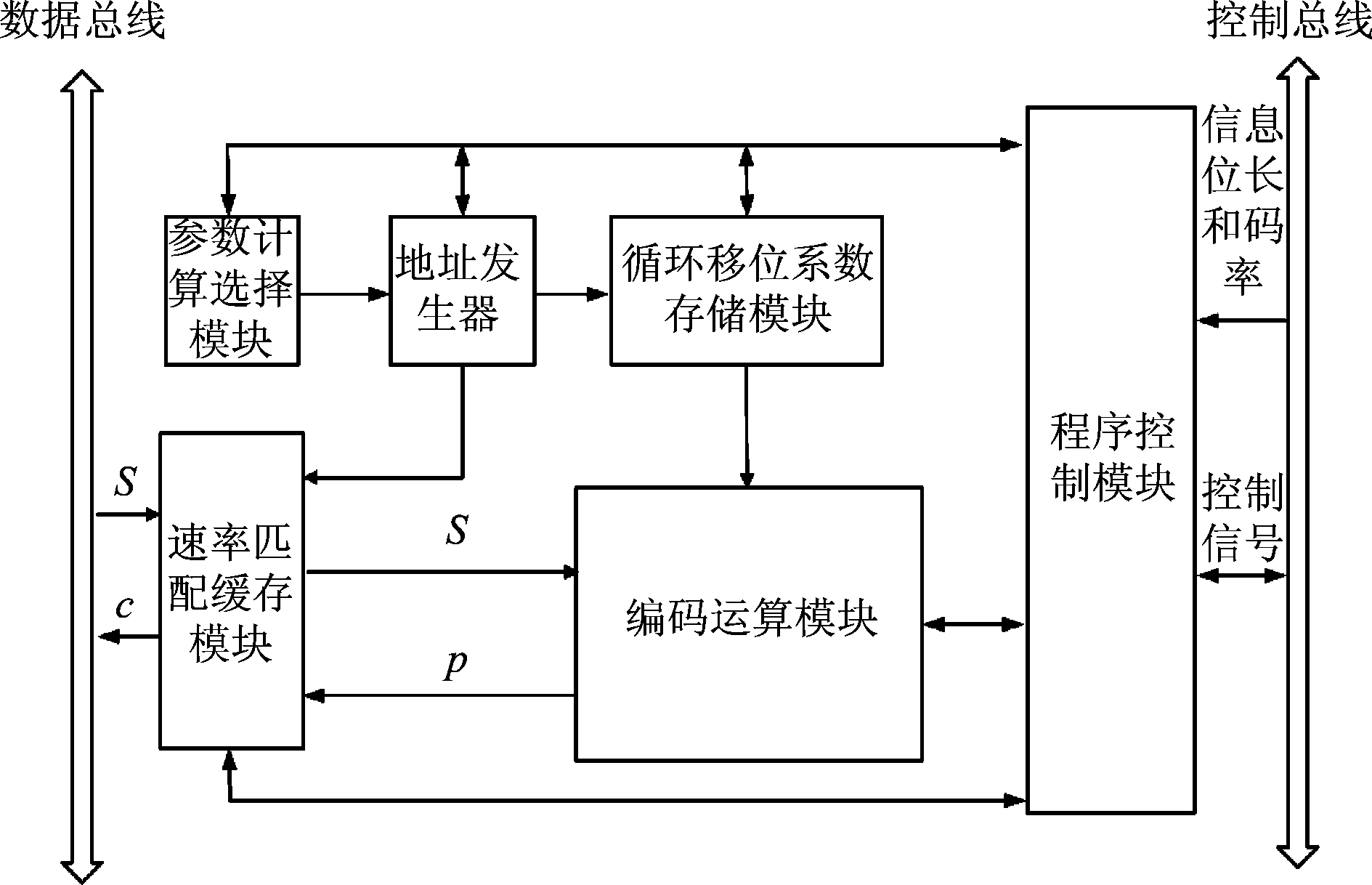

本编码器的整体框架如图3所示,由程序控制模块,参数计算选择模块,速率匹配缓冲模块,循环移位系数存储模块,地址发生器和编码运算模块组成,输入为待编码的信息位和要求的信息位长度,码率以及扩展因子![]() 程序控制模块通过接收总线命令控制模块与总线间,模块与模块间的数据流;参数选择计算模块根据输入的码长和码率计算出所需的编码参数输入地址发生器;地址发生器根据接收到的编码参数产生相应的读写地址提供给循环移位系数存储模块和速率匹配缓冲模块;循环移位系数存储模块存储着PG1和PG2矩阵中的移位系数并根据地址范围选取本次编码使用的校验矩阵块将相应的循环移位值提供给编码运算模块;速率匹配缓冲模块主要由两块双端口RAM组成,负责对信息位的打孔和缩短以及校验位的打孔;编码运算模块为编码器的核心单元,采用多路并行的电路结构根据2.2节提出的高并行度的LDPC码编码算法快速的完成编码。

程序控制模块通过接收总线命令控制模块与总线间,模块与模块间的数据流;参数选择计算模块根据输入的码长和码率计算出所需的编码参数输入地址发生器;地址发生器根据接收到的编码参数产生相应的读写地址提供给循环移位系数存储模块和速率匹配缓冲模块;循环移位系数存储模块存储着PG1和PG2矩阵中的移位系数并根据地址范围选取本次编码使用的校验矩阵块将相应的循环移位值提供给编码运算模块;速率匹配缓冲模块主要由两块双端口RAM组成,负责对信息位的打孔和缩短以及校验位的打孔;编码运算模块为编码器的核心单元,采用多路并行的电路结构根据2.2节提出的高并行度的LDPC码编码算法快速的完成编码。

图3 编码器整体框架示意图

Fig.3 The overall structure of proposed encoder

5G标准通过多样化矩阵参数选择以及灵活的打孔和缩短操作来支持不同的码长和码率,以保证在复杂的信道条件下仍然具有良好的性能,这对编码器实现的灵活性提出了很高的要求。本文采用多种策略确保编码器可以实现对5G标准的全面支持。

在整体结构上串行架构延时过长不适用于对延时要求很高的5G通信系统,又因为5G标准支持的最大信息位长度kmax=8448,采用并行架构会消耗巨大的逻辑资源导致不可实现,所以本编码器采用了最大并行度为![]() 的部分并行结构,各个单元的输入位宽均为最大扩展因子

的部分并行结构,各个单元的输入位宽均为最大扩展因子![]() 信息位从外部输入到速率匹配缓冲模块的输入缓存RAM中并

信息位从外部输入到速率匹配缓冲模块的输入缓存RAM中并![]() 位一组并行输出到编码运算模块,当

位一组并行输出到编码运算模块,当![]() 时,缺省的输入被设为0,这种结构可以使得本编码器兼容5G标准中所有码长的LDPC码,避免了由于传输的码长不同而对编码器进行重新设计的麻烦。

时,缺省的输入被设为0,这种结构可以使得本编码器兼容5G标准中所有码长的LDPC码,避免了由于传输的码长不同而对编码器进行重新设计的麻烦。

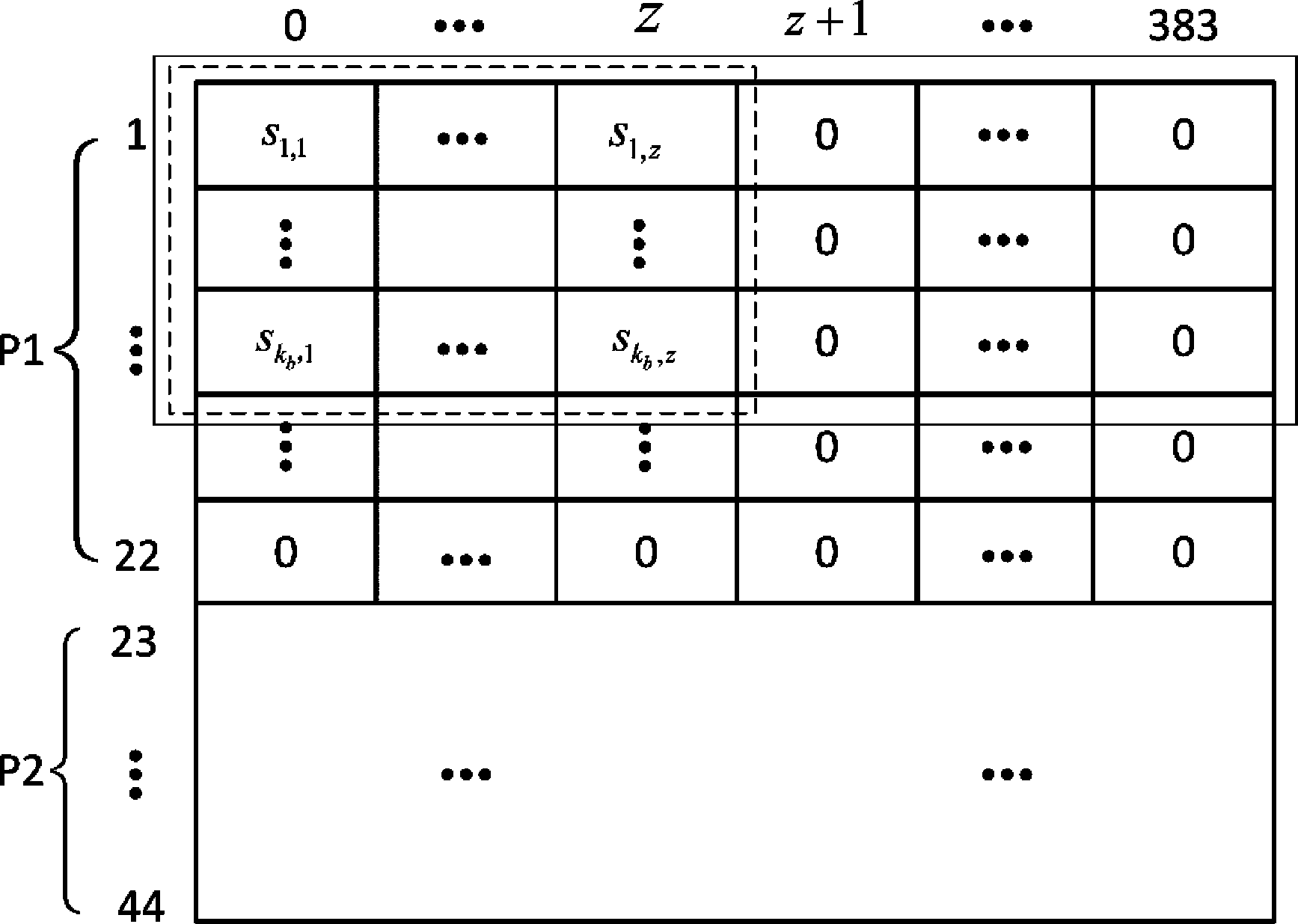

速率匹配缓存模块可以实现信息位的打孔和缩短以及校验位的打孔来匹配不同的信道资源,模块主要由两块双端口RAM组成分别用来缓存输入的信息位和输出的码字。输入缓存RAM的存储结构如图4所示,存储空间按照地址递增的顺序被分为存储深度为22的两部分,每部分可以刚好缓存kmax位的信息位。采用这种结构可以在对当前信息位进行编码的同时读入下一段待编码的信息位,节省了读入的时间,提高了编码器的吞吐率。在每次信息位输入之前输入缓存RAM的所有位置都会被初始化为0并按存储地址被由小到大按照位宽每384分为一组,当输入的信息位数k<kmax时,信息序列按![]() 位分组存储到相应的存储地址组中,例如第一组

位分组存储到相应的存储地址组中,例如第一组![]() 位信息位s1,1到

位信息位s1,1到![]() 存储到地址0到

存储到地址0到![]() 中,第二组信息位s2,1到

中,第二组信息位s2,1到![]() 存储到到地址384到

存储到到地址384到![]() 中以此类推最终分配到红色虚线框区域内。由于存储器此前已经初始化,分组后的信息序列会在存储器中补0至384位,最终蓝色实线框内的序列将会被按行读出。由于0在运算中不会影响实际计算结果,所以只需在编码器的输出端去除这些无关输入产生的输出即可实现对标准中不同长度码字的支持同时在不消耗额外资源的情况下完成了信息位的缩短。输出缓存RAM主要完成信息位和校验位的打孔工作,它接受编码后的完整码字根据地址发生器产生的地址范围舍弃需要打孔的冗余比特和位宽匹配产生的无关比特,输出最终所需的N比特码字完成编码。

中以此类推最终分配到红色虚线框区域内。由于存储器此前已经初始化,分组后的信息序列会在存储器中补0至384位,最终蓝色实线框内的序列将会被按行读出。由于0在运算中不会影响实际计算结果,所以只需在编码器的输出端去除这些无关输入产生的输出即可实现对标准中不同长度码字的支持同时在不消耗额外资源的情况下完成了信息位的缩短。输出缓存RAM主要完成信息位和校验位的打孔工作,它接受编码后的完整码字根据地址发生器产生的地址范围舍弃需要打孔的冗余比特和位宽匹配产生的无关比特,输出最终所需的N比特码字完成编码。

图4 输入缓存RAM的存储结构

Fig.4 Memory organization of Input RAM

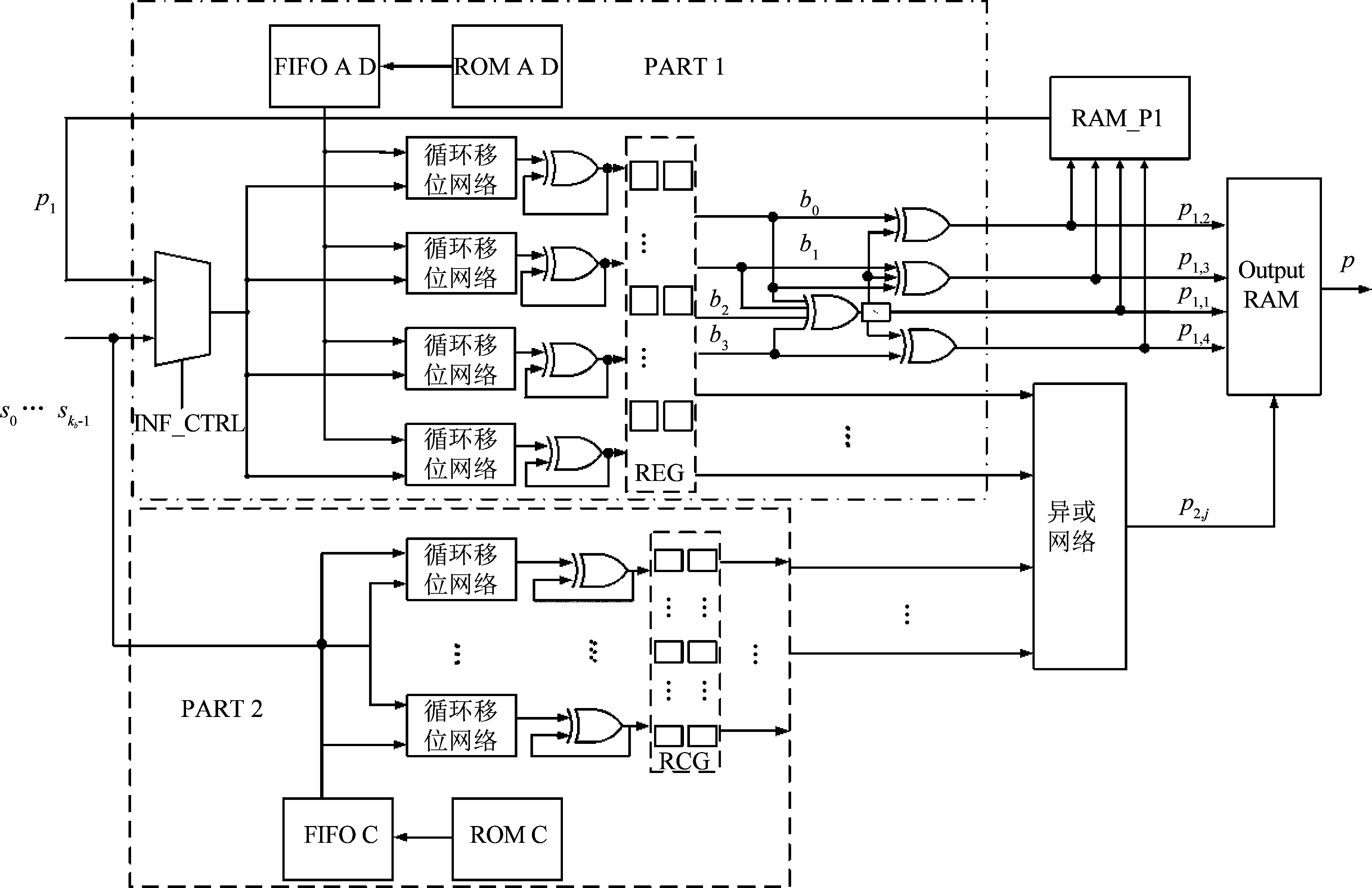

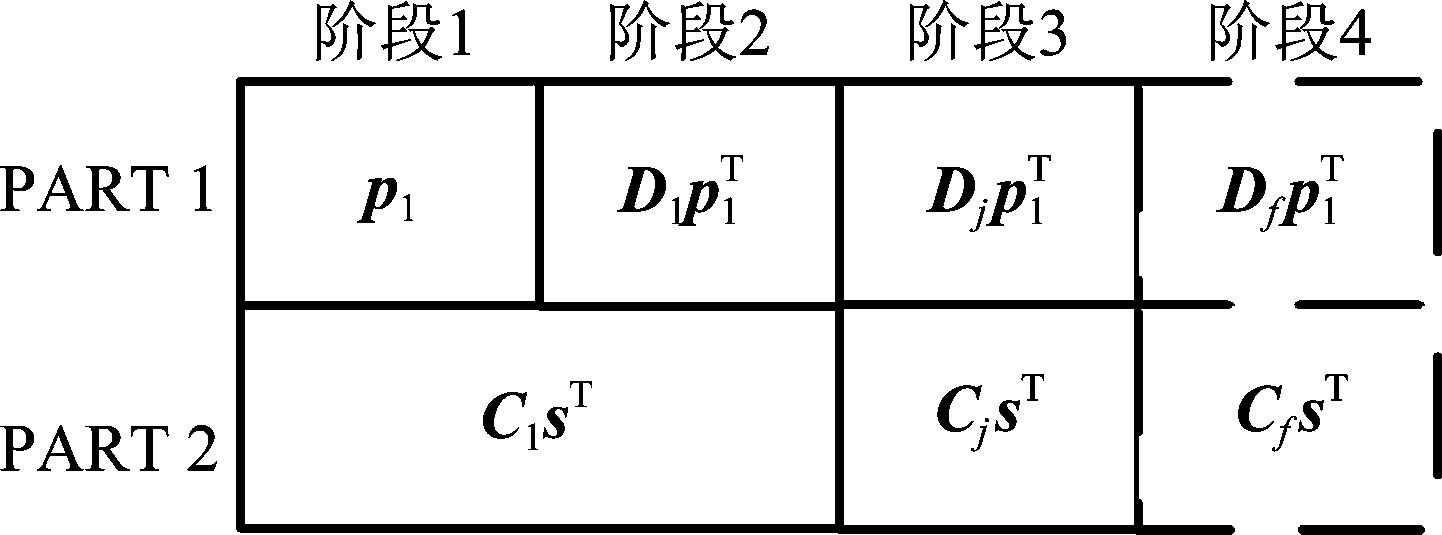

编码运算模块是编码运算的核心单元,采用部分并行结构实现2.2小节提出的高并行度的LDPC码编码算法,模块主要分为PART 1和PART 2两部分,如图5所示。

图5 编码运算模块示意图

Fig.5 The structure of Encoding Unit

PART 1主要完成编码算法第一步中校验位p1和二三步中![]() 的计算,由一个选通网络,两块BLOCK RAM (BRAM),一块FIFO,4个

的计算,由一个选通网络,两块BLOCK RAM (BRAM),一块FIFO,4个![]() 位循环移位网络,多组异或网络和寄存器组组成并被分为四路并行运算,每一路包括一个循环移位网络和与之相连的特定的异或网络和寄存器组。选通网络由多路选择器组成,从信息位序列s和校验位序列p1中选通所需要的序列,当控制信号INF_CTRL为低时将信息位sj(0≤j≤kb-1)作为选通网络的输出每周期并行输入到四个循环移位网络的输入端来计算校验序列p1。想要求得p1首先需要计算中间向量

位循环移位网络,多组异或网络和寄存器组组成并被分为四路并行运算,每一路包括一个循环移位网络和与之相连的特定的异或网络和寄存器组。选通网络由多路选择器组成,从信息位序列s和校验位序列p1中选通所需要的序列,当控制信号INF_CTRL为低时将信息位sj(0≤j≤kb-1)作为选通网络的输出每周期并行输入到四个循环移位网络的输入端来计算校验序列p1。想要求得p1首先需要计算中间向量![]() 将Ai, j对应的循环移位系数和sj同时送入到PART 1中第i路循环移位网络的两个输入端进行简单的循环移位,在输出端即为

将Ai, j对应的循环移位系数和sj同时送入到PART 1中第i路循环移位网络的两个输入端进行简单的循环移位,在输出端即为![]() 的结果。新计算得到的

的结果。新计算得到的![]() 会同此前求得的所有

会同此前求得的所有![]() 的和通过异或网络进行模二加并用新的和值更新寄存器中存储的旧和值直至j=kb-1时完成一轮更新,此时第i路寄存器组中存储的值就是bi。根据式(7)右边方程组推得的关系,由bi通过异或电路和移位电路可同时求得p1的四组分量,但是并行计算p1,1~p1,4需要四组相同的电路来计算(b0+b1+b2+b3)≫1,这样会带来巨大的逻辑资源消耗和过长的关键路径使得设计不可实现,所以我们将这个过程分为三步,第一步求解b0+b1+b2+b3,第二步将求和的结果右移一位求得p1,1,第三步同时求解p1,2,p1,3和p1,4并将它们存入RAM_P1和Output_RAM缓存,控制信号INF_CTRL会在下个周期被程序控制模块拉高,PART 1电路的功能转变为计算

的和通过异或网络进行模二加并用新的和值更新寄存器中存储的旧和值直至j=kb-1时完成一轮更新,此时第i路寄存器组中存储的值就是bi。根据式(7)右边方程组推得的关系,由bi通过异或电路和移位电路可同时求得p1的四组分量,但是并行计算p1,1~p1,4需要四组相同的电路来计算(b0+b1+b2+b3)≫1,这样会带来巨大的逻辑资源消耗和过长的关键路径使得设计不可实现,所以我们将这个过程分为三步,第一步求解b0+b1+b2+b3,第二步将求和的结果右移一位求得p1,1,第三步同时求解p1,2,p1,3和p1,4并将它们存入RAM_P1和Output_RAM缓存,控制信号INF_CTRL会在下个周期被程序控制模块拉高,PART 1电路的功能转变为计算![]() 此时p1,1~p1,4会经由选通网络循环输出,同时ROM_A_D会在第j个循环中每个周期输出Dj中的一列循环移位系数,最终每完成一次p1,1~p1,4循环即可在寄存器组中得到一组

此时p1,1~p1,4会经由选通网络循环输出,同时ROM_A_D会在第j个循环中每个周期输出Dj中的一列循环移位系数,最终每完成一次p1,1~p1,4循环即可在寄存器组中得到一组![]()

PART 2部分的结构和PART 1并行运行且采用同样的四路并行的结构,区别是它只计算Ci·sT所以并不需要选通网络和计算式(7)所需的异或逻辑。虽然编码运算模块的两部分中均采用四路并行的结构,但是考虑采用这种结构的原因并不完全相同,PART 1主要由于p1可以分成四个分量对应校验矩阵的前四行,四采用路并行可以同时计算出4组中间变量b0~b3增加了电路的并行度进而减小了运算时延。而PART 2设计成与PART 1相匹配的结构则考虑到对PART 1部分电路的复用,在保证吞吐率的同时兼顾逻辑资源的利用率。这是因为要求p2的一组分量p2, j同时求出相应的Ci·sT与![]() 才不带来延时,为了复用部分PART 1部分电路同时不增加延时PART 2必须和PART 1部分一样设计成四路并行,这也是算法中矩阵的C,D部分按照每四行进行分块的原因。

才不带来延时,为了复用部分PART 1部分电路同时不增加延时PART 2必须和PART 1部分一样设计成四路并行,这也是算法中矩阵的C,D部分按照每四行进行分块的原因。

编码运算模块的运算过程按照处理状态的不同可以分为4个阶段,如图6所示。前两个阶段和高并行度的LDPC码编码算法中的前两步对应,后两个阶段则完成算法的第三步。在阶段1和阶段2 模块的PART 1部分依次计算得到p1和![]() 与此同时PART 2计算C1sT,由于p1的计算时长大于C1sT,C1sT会在计算完成后暂存等待PART 1得到

与此同时PART 2计算C1sT,由于p1的计算时长大于C1sT,C1sT会在计算完成后暂存等待PART 1得到![]() 的结果,而后C1sT和

的结果,而后C1sT和![]() 同时输入到图5右下方的异或网络中计算

同时输入到图5右下方的异或网络中计算![]() 求出p2的第一组分量p2,1~p2,4。阶段3中PART 1和PART 2分别循环输入p1,1~p1,4和s0~skb-1得到CisT和

求出p2的第一组分量p2,1~p2,4。阶段3中PART 1和PART 2分别循环输入p1,1~p1,4和s0~skb-1得到CisT和![]() 作为异或网络的两组输入,每次循环都可以计算得到p2的一组p2, j直至所有分量都求解完毕。由于信息位的组数kb-1>4,每组

作为异或网络的两组输入,每次循环都可以计算得到p2的一组p2, j直至所有分量都求解完毕。由于信息位的组数kb-1>4,每组![]() 计算完成后需要等待相应的CisT的结果。阶段4和阶段3求解过程基本相同,作用是在本次编码所选取的循环移位矩阵行数不能被4整除时求解

计算完成后需要等待相应的CisT的结果。阶段4和阶段3求解过程基本相同,作用是在本次编码所选取的循环移位矩阵行数不能被4整除时求解![]() 得到p2中最后

得到p2中最后![]() 个分量,rf为Df和Cf的行数。由于这个阶段只有在特定情况下才出现,所以图中用虚线框表示,此时编码运算模块的每部分中只有前rf路使能。

个分量,rf为Df和Cf的行数。由于这个阶段只有在特定情况下才出现,所以图中用虚线框表示,此时编码运算模块的每部分中只有前rf路使能。

设Q1,Q2,Q3分别为循环移位矩阵中A, C1,D1区域,Ci,Dj(i>1, j>1)区域和Cf,Df区域内的元素个数之和。根据上面的计算过程,编码运算模块在前两个阶段中共需要进行Q1次循环移位和![]() 位异或来计算bi(0≤i≤3),C1sT和

位异或来计算bi(0≤i≤3),C1sT和![]() 并需要1次右移和7次

并需要1次右移和7次![]() 位异或和由bi计算得到p1。在后两个阶段中分别需要Q2与Q3次循环移位和

位异或和由bi计算得到p1。在后两个阶段中分别需要Q2与Q3次循环移位和![]() 位异或来计算

位异或来计算![]() 和

和![]() 同时计算

同时计算![]() 还需要(mb-4)/4次

还需要(mb-4)/4次![]() 位异或运算。在不考虑实际电路延迟的理想情况下假设所有运算每次都消耗一个时钟周期,结合电路结构可以分析得到以下结果。在阶段1, 2中采用本文提出的算法流程可以节省C1sT部分的运算时间,前面的Q1次循环移位和

位异或运算。在不考虑实际电路延迟的理想情况下假设所有运算每次都消耗一个时钟周期,结合电路结构可以分析得到以下结果。在阶段1, 2中采用本文提出的算法流程可以节省C1sT部分的运算时间,前面的Q1次循环移位和![]() 位异或运算需要kb+1个时钟周期,后面的异或和右移需要三个时钟周期,总共需要kb+4个时钟周期。在阶段3, 4中又节省了

位异或运算需要kb+1个时钟周期,后面的异或和右移需要三个时钟周期,总共需要kb+4个时钟周期。在阶段3, 4中又节省了![]() 和

和![]() 部分的计算时间,两个阶段共需「(mb-4)/4⎤×kb+2个时钟周期。但是在实际的电路实现中将运算都放在一个时钟周期内是不现实的,因为这会带来为过长的关键路径,所以需要在循环移位网络和异或网络中采用流水线设计来减少关键路径的长度提高编码器的工作频率,由于流水线会带来一定的延时,实际采用本编码器完成一次编码共需要「mb/4⎤×kb+29个时钟周期。相比较而言,文献[17]完成整个编码过程需要kb×mb+4×mb+14个时钟周期,从表达式可以直接看出本设计少了第二项的延迟且第一项为它的1/4,所以在处理延时上本设计有明显优势且码率越低优势越明显。

部分的计算时间,两个阶段共需「(mb-4)/4⎤×kb+2个时钟周期。但是在实际的电路实现中将运算都放在一个时钟周期内是不现实的,因为这会带来为过长的关键路径,所以需要在循环移位网络和异或网络中采用流水线设计来减少关键路径的长度提高编码器的工作频率,由于流水线会带来一定的延时,实际采用本编码器完成一次编码共需要「mb/4⎤×kb+29个时钟周期。相比较而言,文献[17]完成整个编码过程需要kb×mb+4×mb+14个时钟周期,从表达式可以直接看出本设计少了第二项的延迟且第一项为它的1/4,所以在处理延时上本设计有明显优势且码率越低优势越明显。

图6 编码运算模块运算时序图

Fig.6 Timing arrangement in Encoding Unit

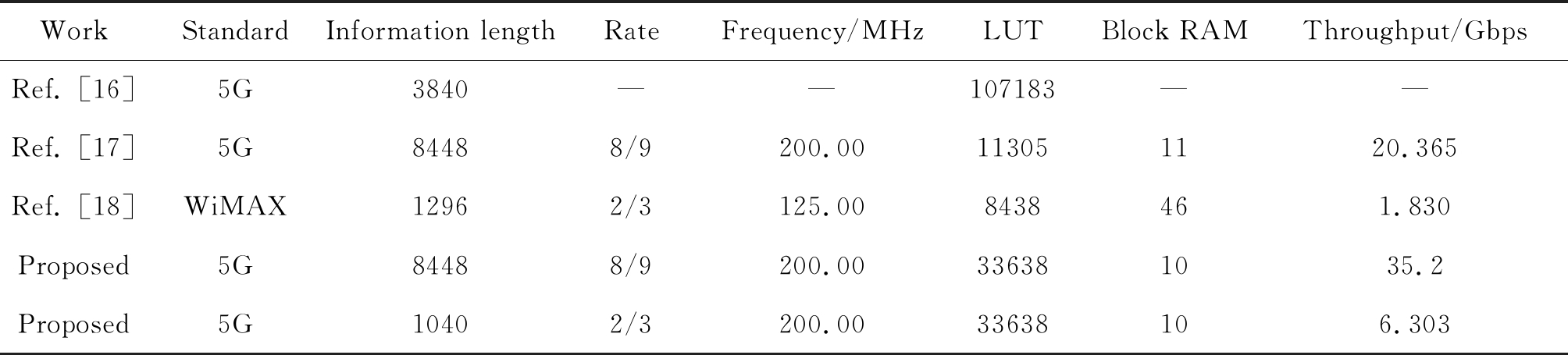

本文所提出的编码器结构对5G标准中的LDPC码进行实现,芯片使用Xilinx公司的XC7VX485T FPGA,在vivado 2018.2平台上进行了逻辑综合和仿真测试。采用384 bit并行输入可满足4 ns的布线布局约束,工作时钟频率可达200 MHz,逻辑资源占用为33638片,并利用了10 块BRAM。本编码器支持多种码长和码率,在信息位长度为8448,码率为8/9 的条件下编码器达到最大吞吐量35.2 Gbps,而在信息位长度为1040,码率为2/3 的条件下编码器的吞吐量为6.303 Gbps,可见本编码器结构可在有限的逻辑资源下达到较高的吞吐量。

表1 QC-LDPC编码器比较

Tab.1 QC-LDPC encoder comparison

WorkStandardInformation lengthRateFrequency/MHzLUTBlock RAMThroughput/GbpsRef. [16]5G3840——107183——Ref. [17]5G84488/9200.00113051120.365Ref. [18]WiMAX12962/3125.008438461.830Proposed5G84488/9200.00336381035.2Proposed5G10402/3200.0033638106.303

表1是本编码器实现结果与文献[16-18]的实现结果的比较。为了比较的公平性,我们对和以上文献中相近的码长与码率进行实现和对比。从表1中可以看出,本设计消耗的逻辑资源为33638片,远少于文献[16]的107183片,虽然相较于文献[17]中的11305 片和[18]中的8438 片较多,但是这是由于本设计采用了四路并行的处理架构,利用较多的逻辑资源达到了更低的处理延时,表现在本设计的吞吐量达到了文献[17]的1.73 倍,更是达到了文献[18]的3.44 倍并且随着编码码率的降低优势将更加明显。可以看出,无论是从编码器的灵活性,处理延时或吞吐量的大小相比,本文所提出的编码器实现架构都更具优势。

本文针对5G标准中结构化的低密度奇偶校验码,通过对算法流程的改进设计了一种高并行度的LDPC码编码算法并利用算法的特性设计了低延时的编码器。编码器通过多路并行的结构来同时计算中间变量和多组校验位,在降低了计算延时的同时也提高了硬件资源的利用率,并提供了对5G标准中多种码长和码率的支持。在Xilinx XC7VX485T FPGA 上的仿真结果表明,本编码器可以较低的延时完成5G标准下LDPC码的编码,吞吐量最高可以达到35.2 Gbps。

[1] Agiwal M, Roy A, Saxena N. Next Generation 5G Wireless Networks: A Comprehensive Survey[J]. IEEE Communications Surveys & Tutorials, 2017, 18(3): 1617-1655.

[2] Serror M, Dombrowski C, Wehrle K, et al. Channel Coding Versus Cooperative ARQ: Reducing Outage Probability in Ultra-Low Latency Wireless Communications[C]∥IEEE Global Telecommunications Conference (GLOBECOM 2015). CA, USA: IEEE, 2015: 1- 6.

[3] Sybis M, Wesolowski K, Jayasinghe K, et al. Channel Coding for Ultra-Reliable Low-Latency Communication in 5G Systems[C]∥Vehicular Technology Conference. QC, Canada: IEEE, 2017: 1-5.

[4] Shannon C E. Communication Theory of Secrecy Systems[J]. The Bell System Technical Journal, 1948, 28(4): 656-715.

[5] Gallager R. Low-density parity-check codes[J]. IRE Transactions on Information Theory, 1962, 8(1): 21-28.

[6] Fossorier M. Quasicyclic low density parity check codes[C]∥IEEE International Symposium on Information Theory. Yokohama, Japan: IEEE, 2003.

[7] 张仲明, 许拔, 杨军, 等. 800Mbps准循环LDPC码译码器的FPGA实现[J]. 信号处理, 2010, 26(2): 255-261.

Zhang Zhongming, Xu Ba, Yang Jun, et al. An 800Mbps Quasi-Cyclic LDPC Decoder Implementation with FPGA[J]. Signal Processing, 2010, 26(2): 255-261.(in Chinese)

[8] Zhang Kai, Huang Xinming, Wang Zhongfeng. High-throughput layered decoder implementation for quasi-cyclic LDPC codes[J]. IEEE Journal on Selected Areas in Communications, 2009, 27(6): 985-994.

[9] Anggraeni S, Hussin F A, Jeoti V. Optimized encoder architecture for structured low density parity check codes of short length[C]∥2014 5th International Conference on Intelligent and Advanced Systems (ICIAS). Kuala Lumpur, Malaysia: IEEE, 2014: 1- 4.

[10] Li Zongwang, Chen Lei, Zeng Lingqi, et al. Efficient encoding of quasi-cyclic low-density parity-check codes[J]. IEEE Transactions on Communications, 2006, 54(1): 71- 81.

[11] Cai Zhaohui, Hao Jianzhong, Tan P H, et al. Efficient encoding of IEEE 802.11n LDPC codes[J]. Electronics Letters, 2006, 42(25): 1471-1472.

[12] Perez J M, Fernandez V. Low-cost encoding of IEEE 802. 11n[J]. Electronics Letters, 2008, 44(4): 1411-1412.

[13] 袁瑞佳, 白宝明, 童胜. 10Gbps LDPC编码器的FPGA设计[J]. 电子与信息学报, 2011, 33(12): 152-157.

Yuan Ruijia, Bai Baoming, Tong Sheng. FPGA-based Design of LDPC Encoder with Throughput over 10 Gbps[J]. Journal of Electronics & Information Technology, 2011, 33(12): 152-157.(in Chinese)

[14] Hamidi-Sepehr F, Nimbalker A, Ermolaev G. Analysis of 5G LDPC Codes Rate-Matching Design[C]∥2018 IEEE 87th Vehicular Technology Conference (VTC Spring). Porto, Portugal: IEEE, 2018: 1-5.

[15] Wu Xiaoning, Jiang Ming, Zhao Chunming, et al. Low-Rate PBRL-LDPC Codes for URLLC in 5G[J]. IEEE Wireless Communications Letters, 2018, 7(5): 800- 803.

[16] 白薇. 5G通信系统中LDPC编译码器的设计与实现[D]. 西安: 西安电子科技大学, 2018.

Bai Wei. Design and Implementation of LDPC Encoder and Decoder for 5G Communication Systems[D]. Xi’an: Xidian University, 2018.(in Chinese)

[17] 黄福威. 5G-LDPC码编译码器设计与FPGA实现技术研究[D]. 西安: 西安电子科技大学, 2019.

Huang Fuwei. Study of Design and FPGA Implementation of 5G-LDPC Code[D]. Xi’an: Xidian University, 2019.(in Chinese)

[18] 刘齐. 码率兼容的LDPC编译码器设计与实现[D]. 成都: 电子科技大学, 2019.

Liu Qi. The Design and Implentation of Rate Compatible LDPC Coder and Decoder[D]. Chengdu: University of Electronic Science and Technology of China, 2019.(in Chinese)

李 赛 男, 1996年生, 河南许昌人。华侨大学信息科学与工程学院硕士研究生, 主要研究方向为信道编码的相关硬件实现、5G移动通信。

E-mail: 954750768@qq.com

周 林(通信作者) 男, 1982年生, 河南南阳人。华侨大学信息科学与工程学院副教授, 硕士生导师, 博士学历。主要研究方向为信道编码与调制、无线通信、光通信等。

E-mail: linzhou@hqu.edu.cn

唐益多 女, 1997年生, 河南平顶山人。华侨大学信息科学与工程学院硕士研究生, 主要研究方向为信道编码与调制、人工智能。

E-mail: duokkxl@sina.com

陈 辰 女, 1990年生, 福建莆田人。华侨大学信息科学与工程学院讲师, 博士学历。主要研究方向为无线通信和信道编码等。

E-mail: 770847349@qq.com

傅玉青 女, 1984年生, 福建泉州人。华侨大学工学院讲师, 硕士生导师, 博士学历。主要研究方向为光通信和信道编码等。

E-mail: fuyq@hqu.edu.cn

贺玉成 男, 1964年生, 山西太原人。华侨大学信息科学与工程学院教授, 硕士生导师, 博士学历。主要研究方向为信道编码与调制、物理层安全通信、协作通信、无线通信网络等。

E-mail: he_yucheng@163.com